A múlt csütörtök elég mozgalmas volt. Felére nem emlékszem már. Viszont arra emlékszem, hogy a munkahelyen fogtam egy vasbogarat (hardware bug). Nézzük csak min is ügyködöm napi 4+ órában:

AEpod

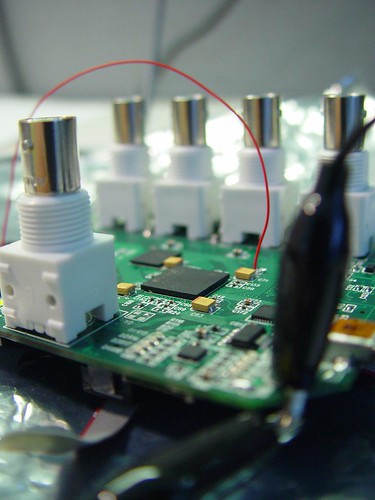

AEpodHidak monitorozásához készítünk alacsony fogyasztású hardvert. Van rajta egy Crossbow Mote, egy Actel IGLOO FPGA, egy jó adag pSRAM, és néhány 3.5 MSPS ADC. Elsősorban az FPGA-ért vagyok felelős, ami nagysebességű mintavételezést és egy nagyon minimális jelfeldogozást végez. A probléma az volt, hogy nem mindig sikerült programozni. Ez elég bosszantó, főleg hogy a programozása egyébként is ~5 percet vesz igénybe. Ráment egy nap, míg kiderült, hogy a JTAG tápvonala kapott egy picit alacsony és instabil táplálást. Gyorsan kerestünk valami közeli stabil forrást és neki is láttam a javításnak. Íme az áthidaló megoldás:

Azóta remekül működik a programozás. Juhéjj!

Azóta remekül működik a programozás. Juhéjj!

Megjegyzés: a VHDL-el kezd kilenni a tököm.

4 megjegyzés:

Igazi mestermunka!!!!

Köszönöm az elismerést.

tenyleg csudaszep :) egyebkent mi a baj a vhdl-el?

Az, hogy a library-k és a különböző konverziós függvények szerintem nincsenek normálisan letisztázva.

Megjegyzés küldése